CS5532

带超低噪音PGIA的16位/24位AD转换器

制造商:

产品信息

CS5531/32/33/34是高集成度的ΔΣ模数转换器,由于运用了电荷平衡技术 , 其性能可以达到16 位(CS5531/33)和24位(CS5532/34)。该系列ADC非常适合测量称重仪表、过程控制、科学和医疗等应用领域的单 /双极性小信号。

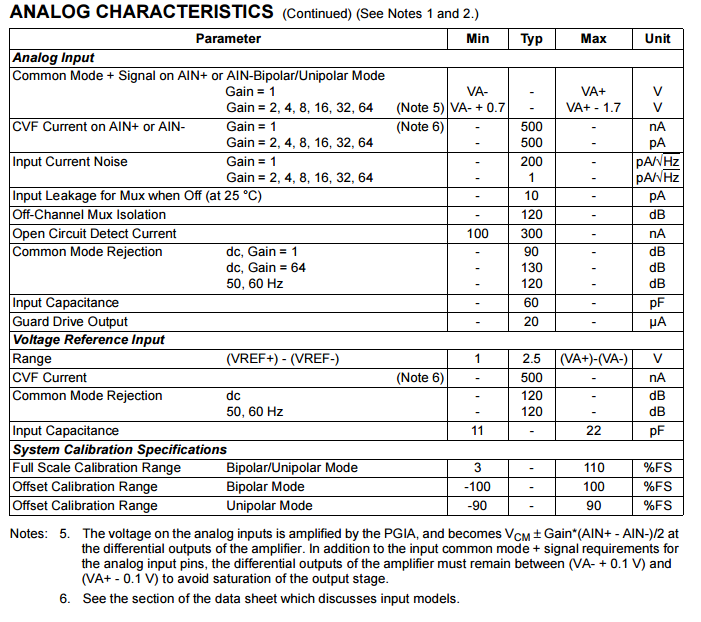

为了适应这些应用,该系列ADC有2通道(CS5531/ 32)或4通道(CS5533/34)可供选择,芯片内部有一个极低噪声的斩波稳定仪表放大器(6nV/ Hz @ 0.1Hz ),其增益可选择为1X、2X、4X、8X、16X、32X及64X。该系列ADCs 内部还有一个4阶的ΔΣ 调制器,其后跟随一个数字滤波器,它提供20种可供选择的输出字速率:6.25、7.5、12.5、 15、25、30、50、60、100、120、200、240、400、480、 800、960、1600、1920、3200及3840Sps(MCLK=4.9152MHz)。

为了方便与微处理器之间的通讯,ADCs内部还有一个与SPI和Microwire 兼容的三线串行接口,在串行时钟口(SCLK)有一个施密特触发器。

高动态范围、可编程输出字速率和灵活的电源配置选项等优点,使得该系列ADCs 成为用于称重仪表和过程控制的理想产品。

优势特点

特性:

Chopper-stabilized PGIA (1x to 64x)

6 nV/√Hz at 0.1 Hz (No 1/f noise) at 64x

500 pA input current with gains >1

Delta-Sigma A/D converter

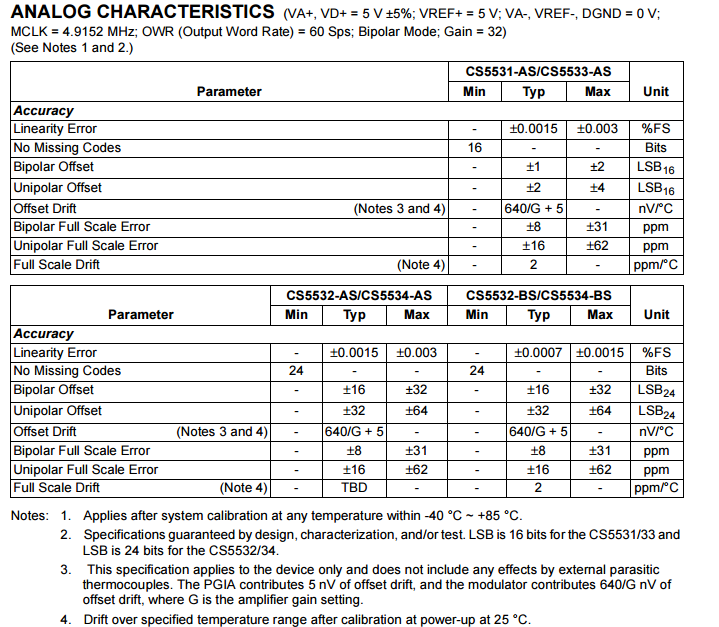

Linearity error: 0.0007% FS

Noise-free resolution: up to 23 bits

2- or 4-channel differential mux

Scalable input span via calibration

± 5 mV to differential ± 2.5 V

Scalable VREF input: up to analog supply

Simple 3-wire serial interface

SPI™ and Microwire™ compatible

Schmitt Trigger on serial clock (SCLK)

Selectable word rates: 6.25 to 3,840 samples per second (SPS)

Selectable 50 Hz or 60 Hz rejection

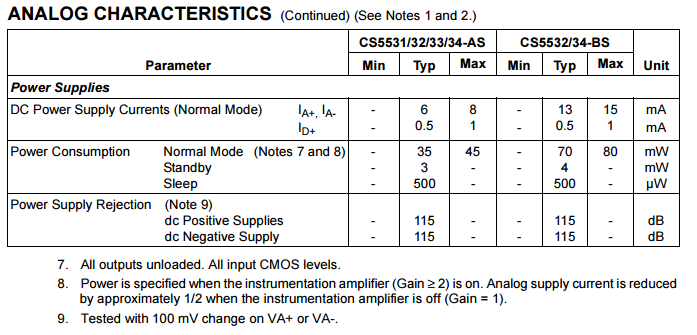

Power supply configurations

VA+ = +5 V; VA- = 0 V; VD+ = +3 V to +5 V

VA+ = +2.5 V; VA- = -2.5 V; VD+ = +3 V to +5 V

VA+ = +3 V; VA- = -3 V; VD+ = +3 V

Package: 20/24-pin SSOP; lead-free assembly

规格参数

电路图、引脚图和封装图

在线购买

型号:CS5532ASZ 管装

描述:-

型号:CS5532BSZ 编带

描述:-

型号:CS5532BSZ

描述:-

型号:CS5532ASZ

描述:-

型号:CS5532-BSR

描述:-

型号:CS5532-BS

描述:-