CD4046

CMOS 微功耗锁相环

制造商:

产品信息

描述:

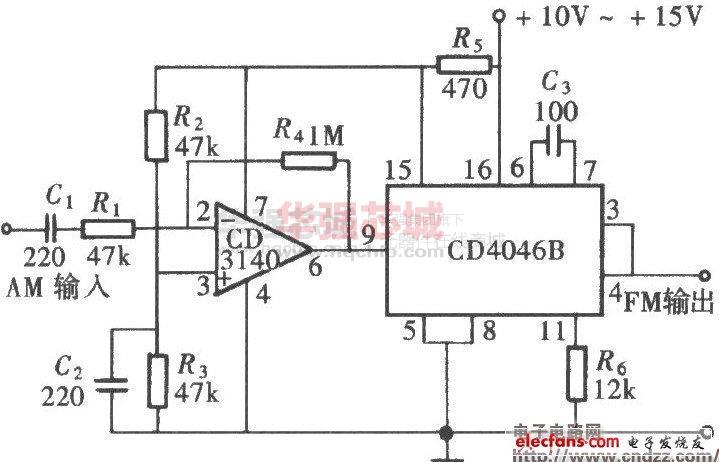

锁相环CC4046为数字PLL,内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。它具有电源电压范围宽、功耗低、输入阻抗高等优点,其工作频率达1MHz,内部VCO 产生50% 占空比的方波,输出电平可与TTL电平或CMOS 电平兼容。同时,它还具有相位锁定状态指示功能。

cD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。本章主要介绍内容有,CD4046的功能 cd4046锁相环电路,CD4046无线发射,cd4046运用,cd4046锁相环电路图。优势特点

特性:

Very low power consumption:

70 µW (typ.) at VCO fo = 10 kHz, VDD = 5 VOperating frequency range up to 1.4 MHz (typ.) at VDD = 10 V, RI = 5 k

Low frequency drift: 0.04%/°C (typ.) at VDD = 10 V

Choice of two phase comparators:

Exclusive-OR network (I)

Edge-controlled memory network with phase-pulse output for lock indication (II)

High VCO linearity:<1% (typ.) at VDD = 10 V

VCO inhibit control for ON-OFF keying and ultra-low standby power consumption

Source-follower output of VCO control input (Demod. output)

Zener diode to assist supply regulation

Standardized, symmetrical output characteristics

100% tested for quiescent current at 20 V

5-V, 10-V, and 15-V parametric ratings

Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

Applications

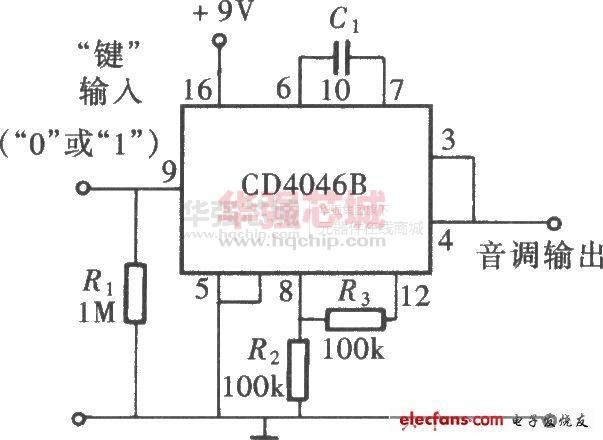

FM demodulator and modulator

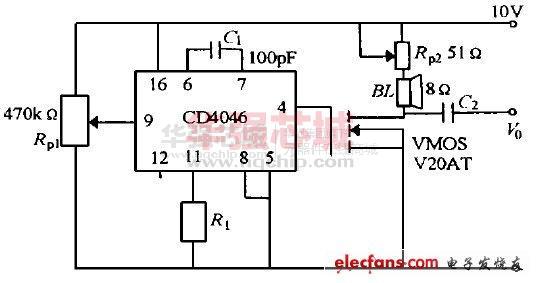

Frequency synthesis and multiplication

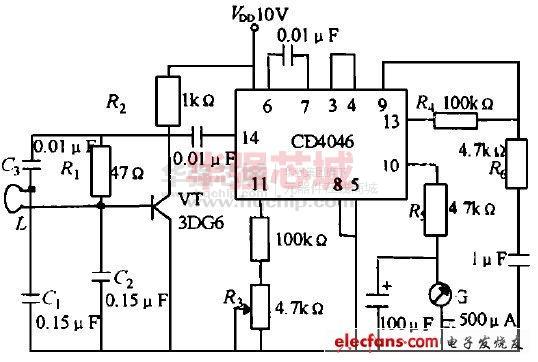

Frequency discriminator

Data synchronization

Voltage-to-frequency conversion

Tone decoding

FSK - Modems

Signal conditioning

(See ICAN-6101) "RCA COS/MOS Phase-Locked Loop - A Versatile Building Block for Micropower Digital and Analog Applications"

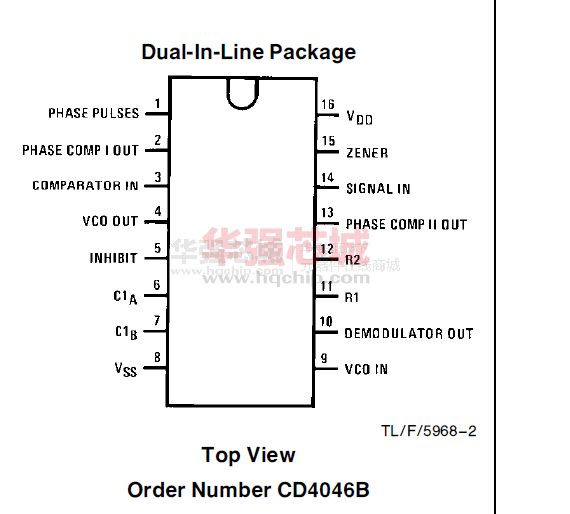

CD4046的引脚排列,采用16脚双列直插式,各管脚功能:

CD4046引脚功能

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

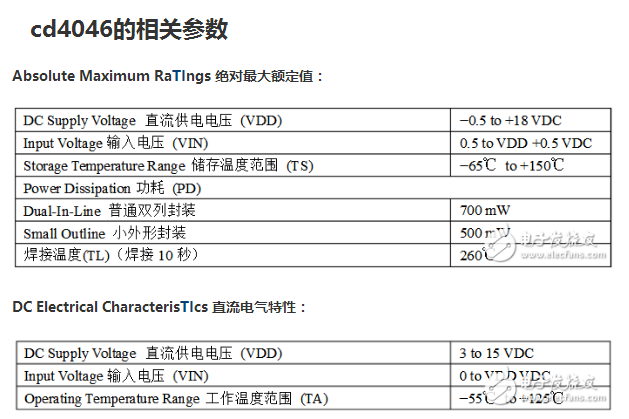

规格参数

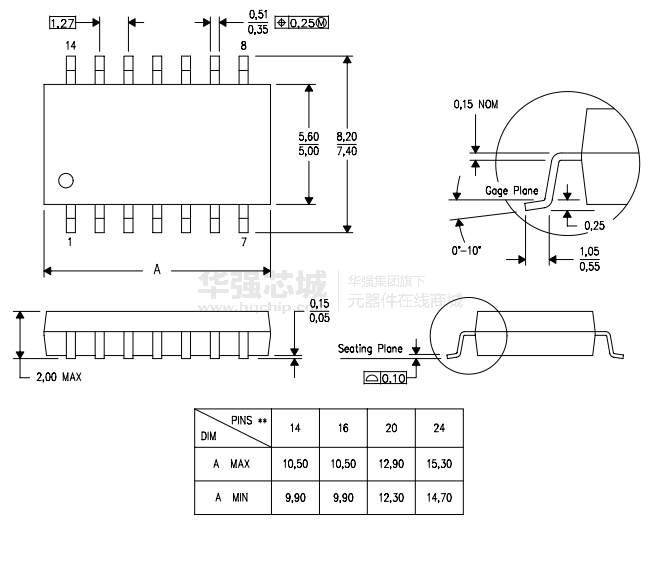

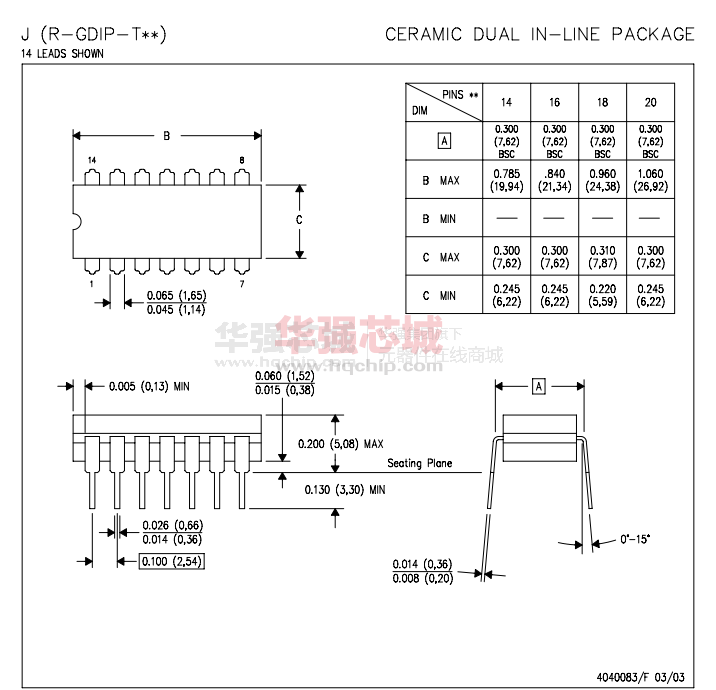

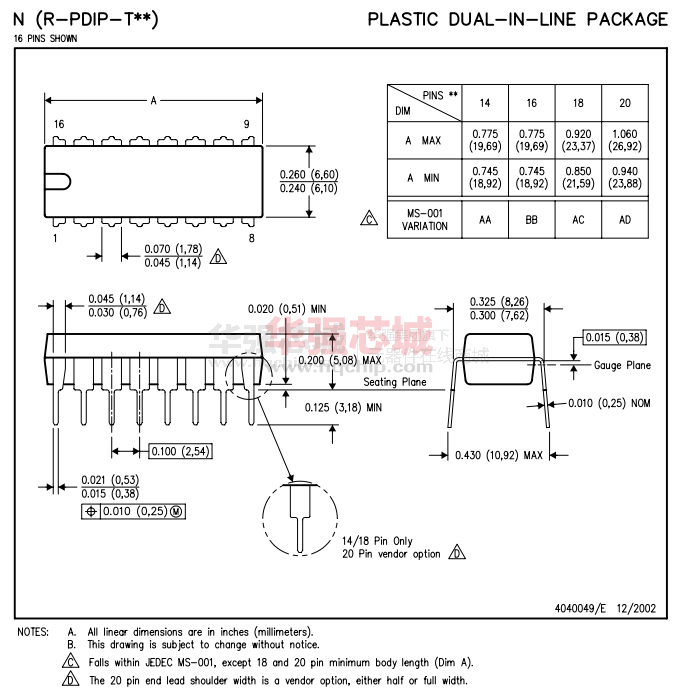

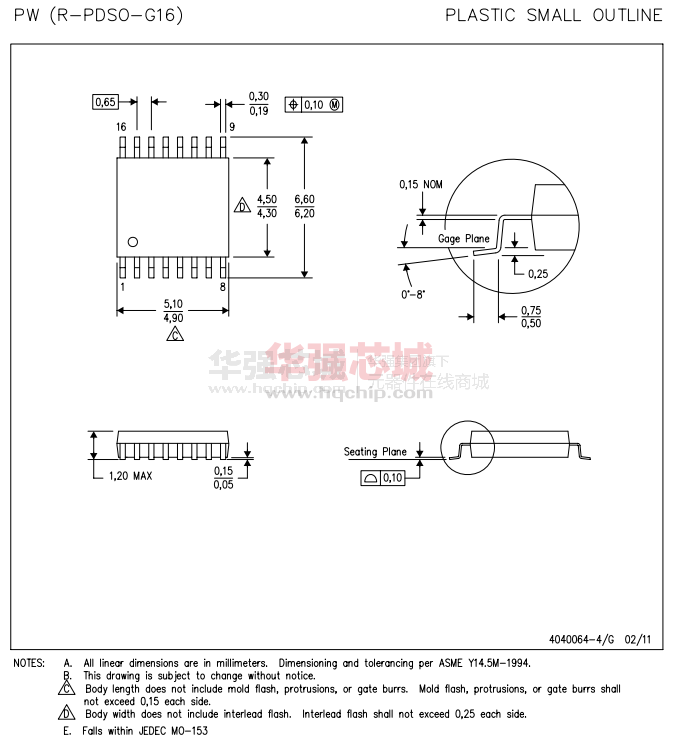

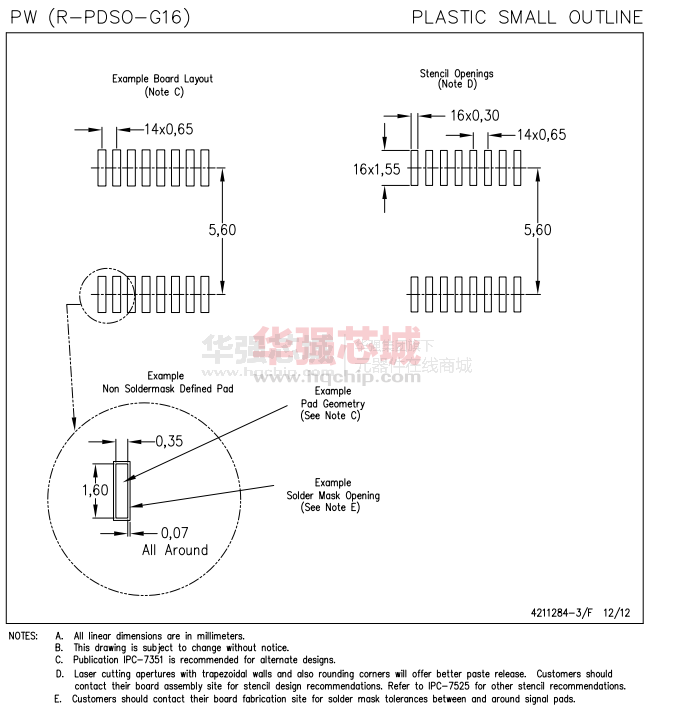

电路图、引脚图和封装图

在线购买

型号:CD4046AK

描述:-

型号:CD4046AF3

描述:-

型号:CD4046AF/3

描述:-

型号:CD4046BF/3A-PKR

描述:-

型号:CD4046BF/3A

描述:-

型号:CD4046BNS

描述:-