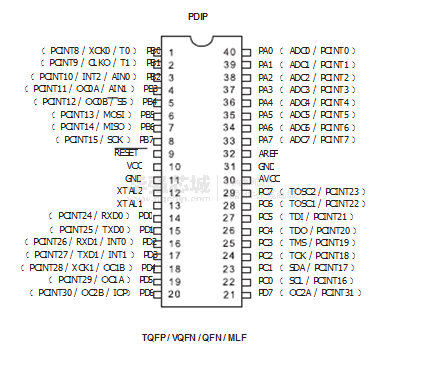

ATMEGA324PA-AU

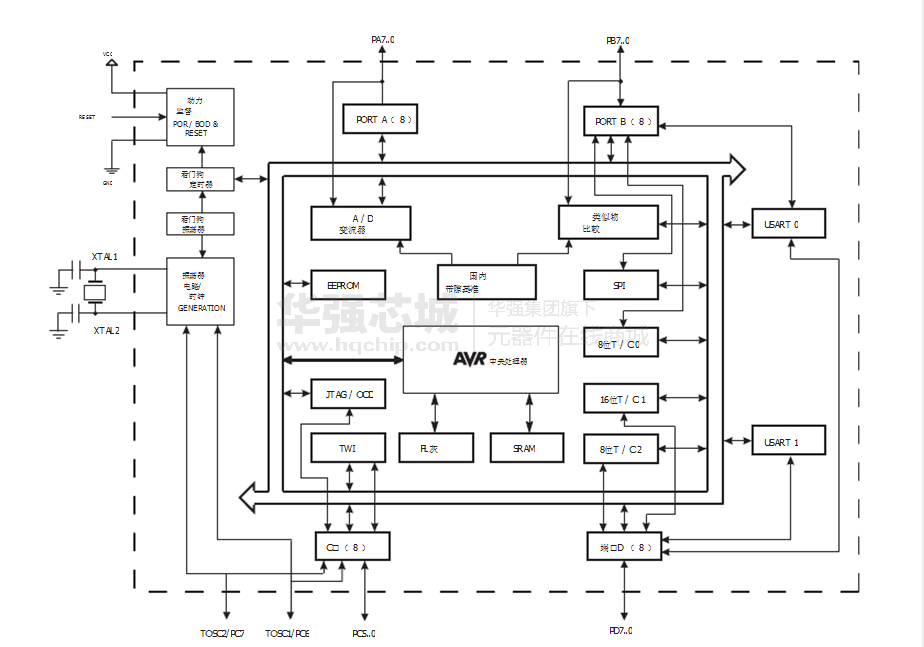

ATmega324PA是一款基于AVR的低功耗8位CMOS微控制器增强的RISC架构。

制造商:

产品信息

特点

•高性能,低功耗的AVR®8位微控制器

•先进的RISC架构

- 131条指令 - 绝大多数为单时钟周期执行

- 32个8位通用工作寄存器

•全静态工作

- 高达20 MIPS的吞吐量,在20兆赫

- 片上2周期乘法器

高耐用性非易失性内存段

- 对在系统内可编程闪存程序存储器32K字节

- 1K字节EEPROM

- 2K字节的片内SRAM

- 写/擦除周期:10,000闪存/ EEPROM 100000

- 数据保存: / 20年85°C百年,在25℃

(1)

- 可选Boot代码区具有独立锁定位

在系统编程通过片上引导程序

真正的同时读 - 写操作

- 可以对锁定的软件安全

JTAG ( IEEE 1149.1标准兼容)接口

- 边界扫描功能根据JTAG标准

- 广泛的片上调试支持

- 对Flash , EEPROM ,熔丝位和锁定位通过JTAG接口编程

外设特性

- 两个8位定时器/计数器具有独立预分频器和比较模式

- 1个16位定时器/计数器具有独立预分频器,比较功能和捕捉模式

- 实时计数器具有独立振荡器

- 六个PWM通道

- 8通道, 10位ADC

差分模式下,可选择增益为1倍, 10倍或200倍

- 面向字节的两线串行接口

- 两个可编程的串行USART

- 主/从SPI串行接口

- 可编程看门狗定时器具有独立的片上振荡器

- 片上模拟比较器

- 中断和唤醒引脚电平变化

单片机特性

- 上电复位和可编程欠压检测

- 内部标定RC振荡器

- 外部和内部中断源

- 六个睡眠模式:空闲模式, ADC噪声抑制,省电,掉电,待机和

延长待机