ADSP-SC582

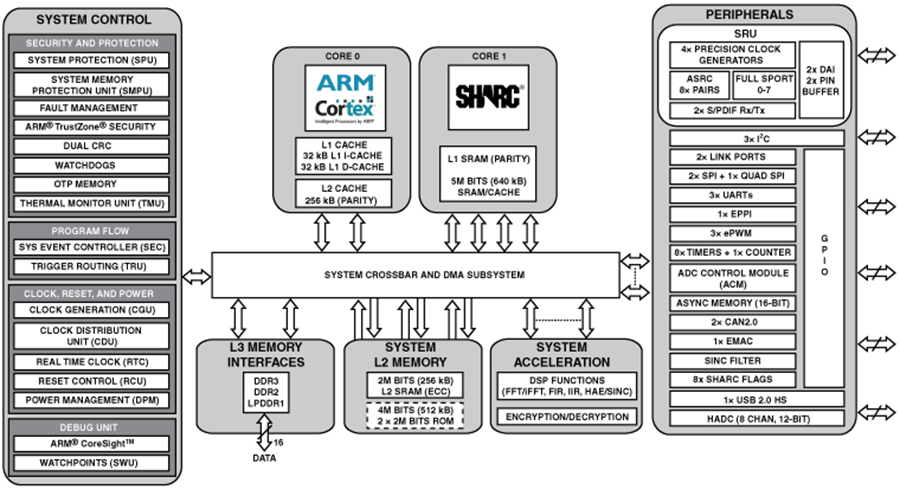

单核SHARC+和ARM Cortex-A5 SOC、DDR、以太网、USB、349-cspBGA

制造商:ADI/AD

产品信息

优势和特点

双核SHARC+基础架构:每个内核450 MHz (2.7GFLOPS)

支持奇偶校验的5Mb/640KB L1存储器/内核

可选缓存/SRAM模式

支持32、40和64位浮点

ARM内核基础架构:450 MHz ARM Cortex-A5(具有Neon/FPU)

32kByte/32kByte L1指令/数据缓存

256kByte L2缓存

共享的系统存储器256KB L2 SRAM,带ECC保护功能

一个速度存储控制器DDR3-900、DDR2-800和LPDDR(16位)

高级硬件加速器FFT/iFFT(18 GFLOPS,每个1K-pt FFT 5usec)

FIR/IIR和SINC滤波器、ASRC

带OTP的安全加密引擎

封装19mm x 19mm BGA(0.8mm间距)

商用、工业

主要连接和接口:千兆以太网MAC (RGMII)

支持IEEE-1588和AVB(QoS和时钟恢复)

USB2.0 HS OTG/设备控制器(MAC/PHY)

2个CAN2.0

最多8个全SPORT接口(提供TDM和I2S模式)

S/PDIF Tx/Rx、8个ASRC对、PCG

2个双通道SPI和1个四通道SPI(提供直接执行功能)

3个 I2C 和 3个UART(提供流量控制功能)

增强型并行外设接口

用于视频I/O或并行转换器接口

2个链路端口(双向、8位、最高150MB/sec)

3个增强型PWM、ADC控制模块(ACM)

8个GP定时器、1个GP计数器、WDT和RTC

最多80个GPIO(多路复用,带其它接口)

8通道12位1MSPS一般管理ADC

热传感器

SHARC+内核基础架构

欲获取ADSP-SC582样片,请订购ADSP-SC584-ENG。请联系当地的 ADI销售部门或经销商办事处。

ADSP-SC58x和ADSP-2158x系列: 总结和比较

电路图、引脚图和封装图

技术资料

EE-400: Using Cache on ADSP-SC5xx/ADSP-215xx SHARC+ Processors (Rev. 1)

EE-392: Estimating Power for ADSP-SC58x/2158x SHARC+ Processors (Rev. 1)

EE-386: Using the Security Packet Engine to Protect Data (Rev. 1)

EE-375: Migrating Legacy SHARC to ADSP-SC58x/2158x SHARC+ Processors (Rev. 1)

EE-378: Processor Comparison Guide (ADSP-BF60x/BF70x vs ADSP-SC58x/2158x) (Rev. 1)

应用案例

TSX582双通道高电流运算放大器深度技术解析

2025-10-24

高灵敏度锁存型霍尔传感器SC2440/SC2442/SC2446/2023-03-20

双USB 蓝牙 MCU芯片 CH583/CH582/CH581引脚信息 跟异同

2022-10-27

意法半导体推出TSB582双路高输出放大器

2022-08-25

什么是SC接口光模块,它有哪些分类

2021-09-08

什么是SC接口光模块,它的分类有哪些

2021-09-08

Analog Devices Inc. ADSPSC835W-EV-SOM模块化系统 (SOM) 板数据手册

2025-05-27

RDC SC2121、SC2161有效提升新能源汽车加速稳定性

2024-05-13