ADRF6821

450 MHz 到 2800 MHz,具有集成式小数分频 PLL 和 VCO 的 DPD RFIC

制造商:ADI/AD

产品信息

优势和特点

具有集成式小数分频 PLL 的 DPD 接收器

RF 输入频率范围:450 MHz 到 2800 MHz

内部 LO 输入频率范围:450 MHz 到 2800 MHz

双 RF 输入具有 SPDT 吸收式 RF 开关

集成式 RF balun 适用于单端 50 Ω 输入

集成式 VCO 可覆盖整个 RF 输入范围

数字可编程 LO 相位偏移和 dc 调零

可通过 4 线 SPI 编程

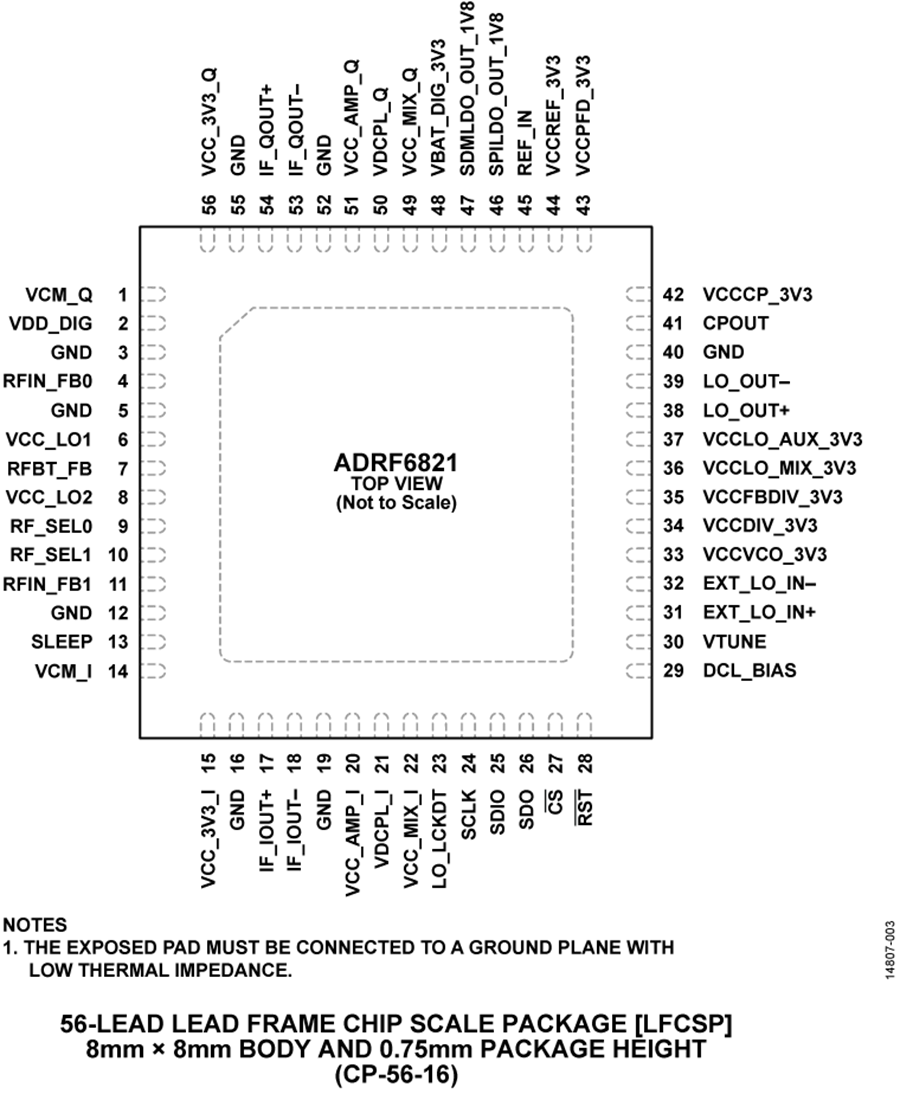

56 引脚 8 mm × 8 mm LFCSP

产品详情

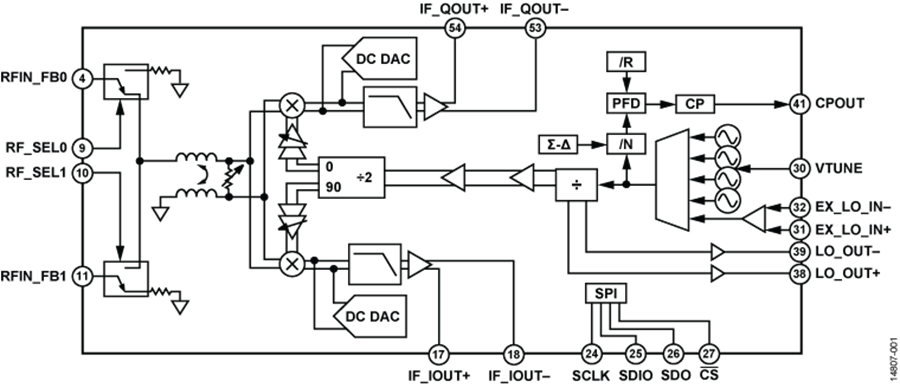

ADRF6821 是一种高度集成的双射频 (RF) 输入、零中频 (IF)/低 IF RFIC 接收器,具有正交解调器、数字步进衰减器 (DSA)、IF 线性放大器、集成式小数分频锁相环 (PLL) 和低相位噪声多核压控振荡器 (VCO)。RFIC 非常适合数字预失真 (DPD) 系统通信。

ADRF6821 配有高度隔离的 2:1 RF 开关和片内宽带 RF balun,支持两个单端 50 Ω 终止 RF 输入。可编程衰减器确保高线性度解调器内核具有最佳的差分 RF 输入电平。集成衰减器提供 15 dB 的衰减范围,步进大小为 1 dB。高线性度 IF 放大器跟在解调器之后,为链中的下一元件 — 通常是模数转换器 (ADC) — 提供接口。

ADRF6821 提供两种生成差分本地振荡器 (LO) 输入信号的方法:通过具有低相位噪声 VCO 的片内小数分频频率合成器在内部生成,或通过相位噪声 LO 信号在外部生成。集成合成器的连续 LO 覆盖范围为 450 MHz 到 2800 MHz。PLL 基准输入支持频率范围宽广,并且在相位频率检测器 (PFD) 之前有一个集成的基准分频器。

选择之后,内部小数分频频率合成器的输出由正交相位分路器分成 2 部分。从外部 LO 路径生成时,2× LO 信号可由正交相位分路器分成 2 部分,以生成混频器的正交 LO 输入。

ADRF6821 通过高级硅锗 (SiGe)、双极互补金属氧化物半导体 (BiCMOS) 工艺制成,采用符合 RoHS 的 56 引脚、8 mm × 8 mm LFCSP 封装以及裸焊盘。性能是在 −40°C 至 +105°C 温度范围内标称。

应用

蜂窝 W-CDMA/GSM/LTE

DPD 接收器

微波点对点无线电

电路图、引脚图和封装图

应用案例

ADRF6820是一款高度集成的解调器和频率合成器

2022-11-15

ADRF5720数字衰减器的性能特点及应用介绍

2019-07-31

基于ADRF5519的主要特性、测试建立图和功能介绍

2021-06-12

ADRF6780 5.9 GHz至23.6GHz、宽带微波上变频器技术手册

2025-03-01

ADRF6821 450MHz到2800MHz,具有集成式小数分频PLL和VCO的DPD RFIC技术手册

2025-02-28

ADRF5026 100MHz至44GHz硅SPDT非反射开关技术手册

2025-03-05

ADBMS6821/ADBMS6822收发器 利用匹配的拉电流和灌电流驱动差分信号,无需变压器中心抽头并降低了电磁干扰

2024-12-10

ADRF5019 100MHz至13 GHz硅SPDT非反射式开关技术手册

2025-03-05