ADRF6620

700 MHz 至 2700 MHz接收混频器,集成IF DGA、小数N分频PLL和VCO

制造商:ADI/AD

产品信息

优势和特点

集成式小数N分频锁相环(PLL)

RF输入频率范围:700 MHz至2,700 MHz

内部本振(LO)频率范围:350 MHz至2,850 MHz

输入P1dB:17 dBm

输出IP3:45 dBm

单刀四掷(SP4T) RF输入开关

数字步进衰减器(DSA)范围:0 dB至15 dB

集成式RF可调谐巴伦,允许单端50 Ω输入

多核集成式压控振荡器(VCO)

数字可编程可变增益放大器(DGA) −3 dB带宽:>600 MHz

150 Ω IF输出平衡阻抗

可通过三线式串行端口接口(SPI)进行编程

5 V单电源

产品详情

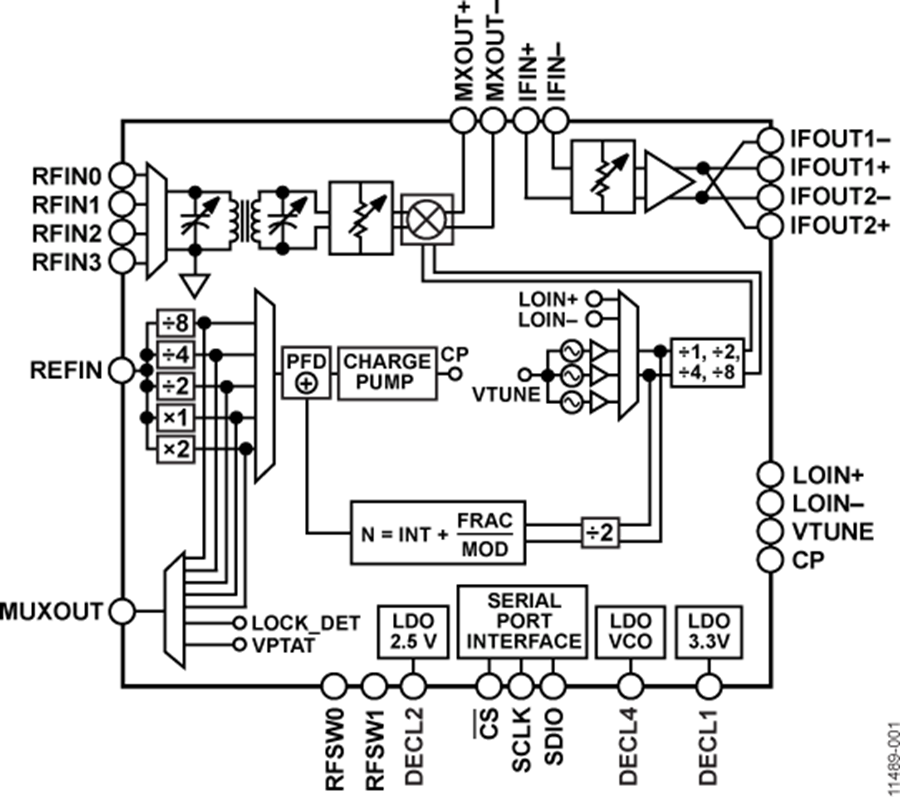

ADRF6620是一款高度集成的有源混频器和频率合成器,非常适合用于无线接收器子系统中。该器件功能丰富,内置一个高线性度宽带有源混频器、一个集成式小数N分频PLL、低相位噪声多核VCO,以及IF DGA。此外,ADRF6620还集成了4:1 RF开关、一个片内可调谐RF巴伦、可编程RF衰减器和低压差(LDO)稳压器。该高度集成的器件适用于7 mm × 7 mm小尺寸解决方案。高度隔离的4:1 RF开关和片内可调谐RF巴伦使ADRF6620支持4个单端50 Ω端接RF输入。可编程衰减器确保高线性度混频器内核具有最佳的RF输入驱动电平。集成式DSA提供的衰减范围为0 dB至15 dB,步进为1 dB。

ADRF6620提供两种备用方式产生差分LO输入信号:从外部通过高频低相位噪声LO信号产生,或从内部通过片内小数N分频PLL频率合成器产生。集成式频率合成器的连续LO覆盖范围为350 MHz至2850 MHz。由于基准频率值在传递至鉴频鉴相器(PFD)之前能够通过除法和乘法模块将其增加或减少至期望值,因此PPL基准电压源输入可支持较宽的频率范围。

集成式高线性度DGA以0.5 dB的步进提供3 dB至15 dB的额外增益范围,驱动模数转换器(ADC)时灵活性极高。

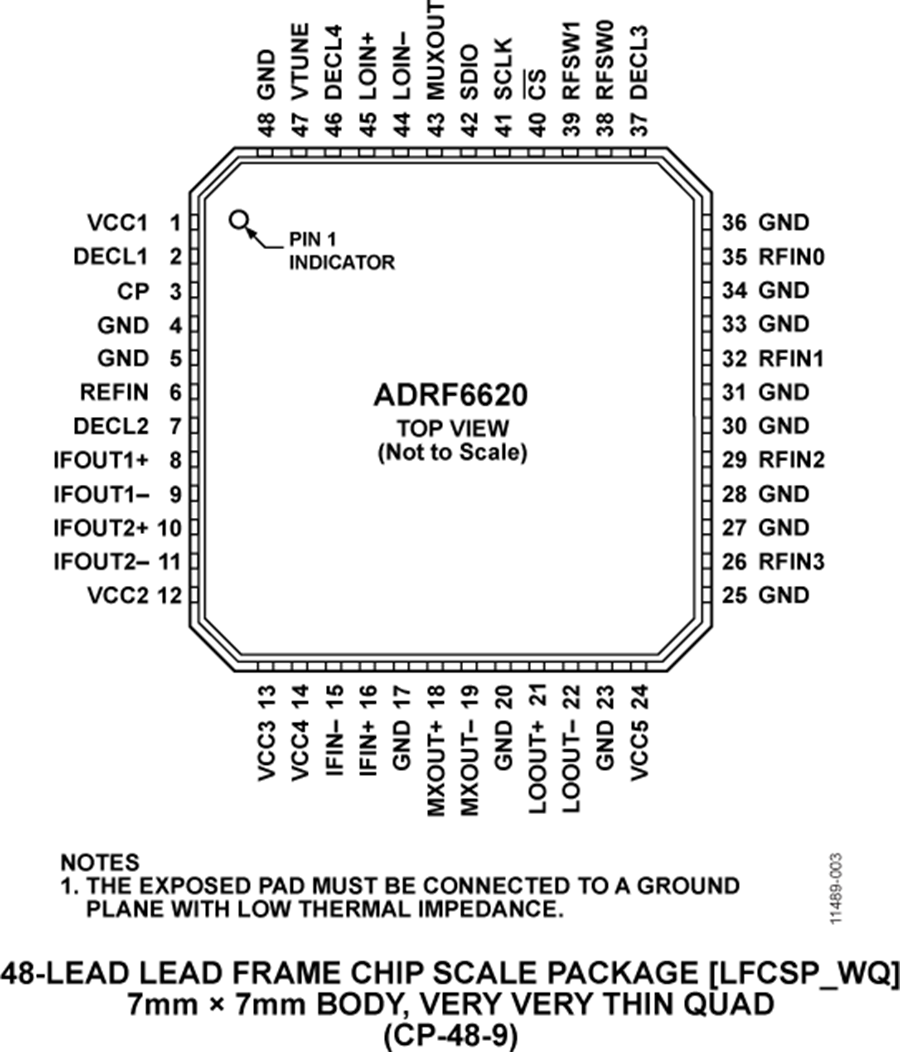

ADRF6620采用先进的硅锗BiCMOS工艺制造,提供48引脚、裸露焊盘、符合RoHS标准的7 mm x 7 mm LFCSP封装。额定温度范围为−40°C至+85°C。

应用

无线接收器

数字预失真(DPD)接收器

电路图、引脚图和封装图

在线购买

型号:ADRF6620ACPZ-R7

描述:-

应用案例

Analog Devices Inc. ADRF5030-EVALZ 评估板数据手册

2025-06-03

Analog Devices Inc. ADRF5301 SPDT开关评估板特性/应用/示意图

2025-06-18

ADRF5130/ADRF5020硅开关产品系列新产品

2019-06-28

Analog Devices Inc. ADRF5048-EVALZ评估板数据手册

2025-06-12

ADRF5130反射式开关介绍

2023-03-01

Analog Devices Inc. ADRF5022-EVALZ 评估板数据手册

2025-06-11

联发科技推出无线连接四合一单芯片MT6620

2011-07-22

20W PD快充芯片U6620S介绍

2023-04-12