ADRF6601

750 MHz至1160 MHz接收混频器,集成小数N分频PLL和VCO

制造商:ADI/AD

产品信息

优势和特点

集成小数N分频PLL的接收混频器

RF输入频率范围:300 MHz至2500 MHz

内部LO频率范围:750 MHz至1160 MHz

输入P1dB:14.5 dBm

输入IP3:31 dBm

通过外部引脚优化IIP3

SSB噪声系数IP3SET引脚断开:13.5 dBIP3SET引脚接3.3 V电压:14.6 dB

电压转换增益:6.7 dB

200 Ω IF输出匹配阻抗

IF 3 dB带宽:500 MHz

可通过三线式SPI接口进行编程

40引脚、6 mm × 6 mm LFCSP封装

产品详情

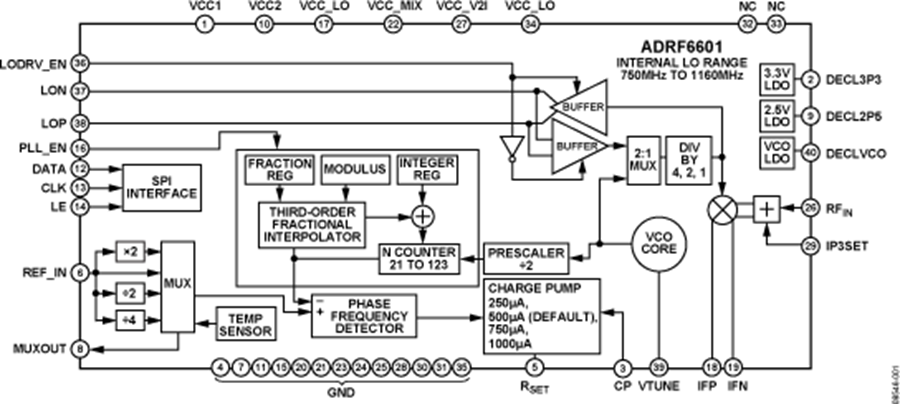

ADRF6601是一款高动态范围有源混频器,集成锁相环(PLL)和压控振荡器(VCO)。PLL/频率合成器利用小数N分频PLL产生fLO输入,供给混频器。基准输入可以进行分频或倍频,然后施加于PLL鉴频鉴相器(PFD)。

PLL支持12 MHz至160 MHz范围内的输入基准频率。PFD输出控制一个电荷泵,其输出驱动一个片外环路滤波器。

然后,环路滤波器输出施加于一个集成式VCO。VCO输出(2 × fLO)再施加于一个LO分频器和一个可编程PLL分频器。可编程PLL分频器由一个Σ-Δ调制器(SDM)进行控制。SDM的模数可以在1至2047范围内编程。

有源混频器可将单端50 Ω RF输入转换为200 Ω差分IF输出。IF输出的工作频率最高可达500 MHz。

ADRF6601采用先进的硅锗BiCMOS工艺制造,提供40引脚、裸露焊盘、符合RoHS标准的6 mm x 6 mm LFCSP封装。额定温度范围为−40°C至+85°C。

应用

蜂窝基站

电路图、引脚图和封装图

在线购买

型号:ADRF6601ACPZ-R7

描述:-

应用案例

LPWAN SOC无线通信芯片ASR6601介绍

2022-03-29

LPWAN低功耗广域网无线通信SoC芯片ASR6601简介

2022-03-10

ASR6601是完整意义的LPWAN SOC无线通信芯片

2021-12-02

ADRF5720数字衰减器的性能特点及应用介绍

2019-07-31

HL6601兼容FP6601 USB Type-A口 快充方案

2024-06-26

基于ADRF5519的主要特性、测试建立图和功能介绍

2021-06-12

解析多普勒雷达信号处理芯片HS6601RD 附3.8GHz雷达信号的电路结构图

2025-04-13

小米盒子3增强版正式上市 安兔兔跑分达到了66015分

2018-04-18