ADP5134ACPZ-R7

微型PMU与1.2 A降压稳压器。

制造商:

产品信息

概述

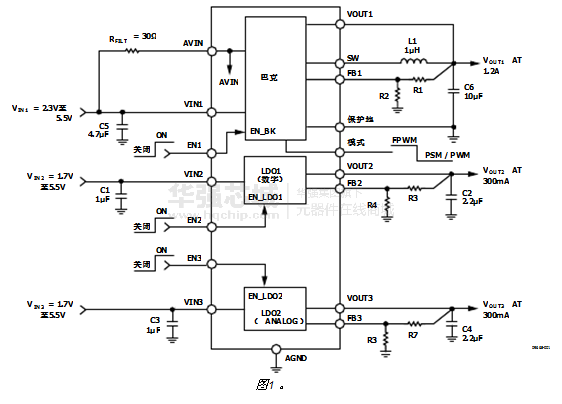

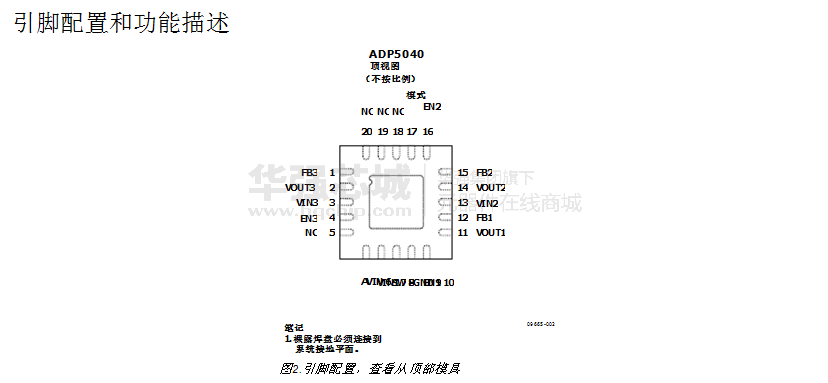

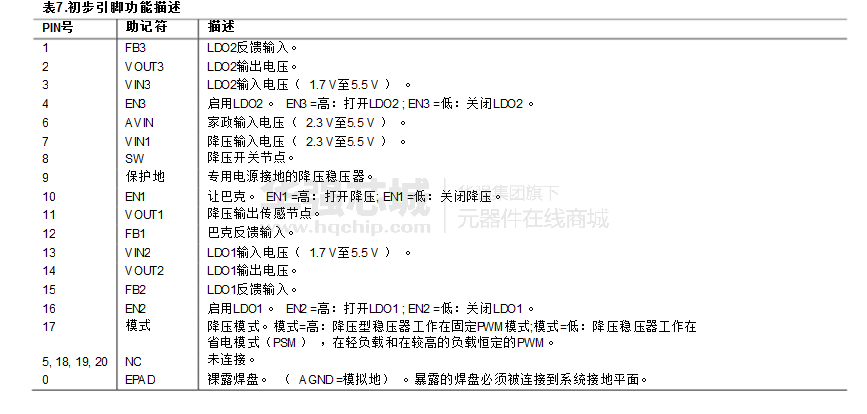

该ADP5040结合了一台高性能降压稳压器和两个低压降稳压器( LDO ),一个小型的20引脚LFCSP封装,以满足严苛的性能和电路板空间要求。

降压调节器的高开关频率允许使用小型多层外部器件,减少电路板空间。当MODE引脚设置为逻辑高电平时,降压稳压器工作在强制脉冲宽度调制(PWM )模式。当MODE引脚设置为逻辑低电平时,降压稳压器以PWM模式工作时的负荷是围绕标称值。当负载电流下降到低于预定阈值稳压器以省电模式( PSM )工作改善的轻负载效率。低静态电流,低压差电压,并在宽输入电压范围LDO的延长便携设备的电池寿命。该LDO能保持电源抑制大于60分贝频率高达10kHz的同时用低净空操作电压。

在每个稳压器ADP5040由一个高级别上激活各自的使能引脚。调节器的输出电压被编程虽然外部电阻分压器,以解决各种应用程序。

特点

1.输入电压范围: 2.3 V至5.5 V

2.一个1.2 A降压稳压器

3.两个300毫安的LDO

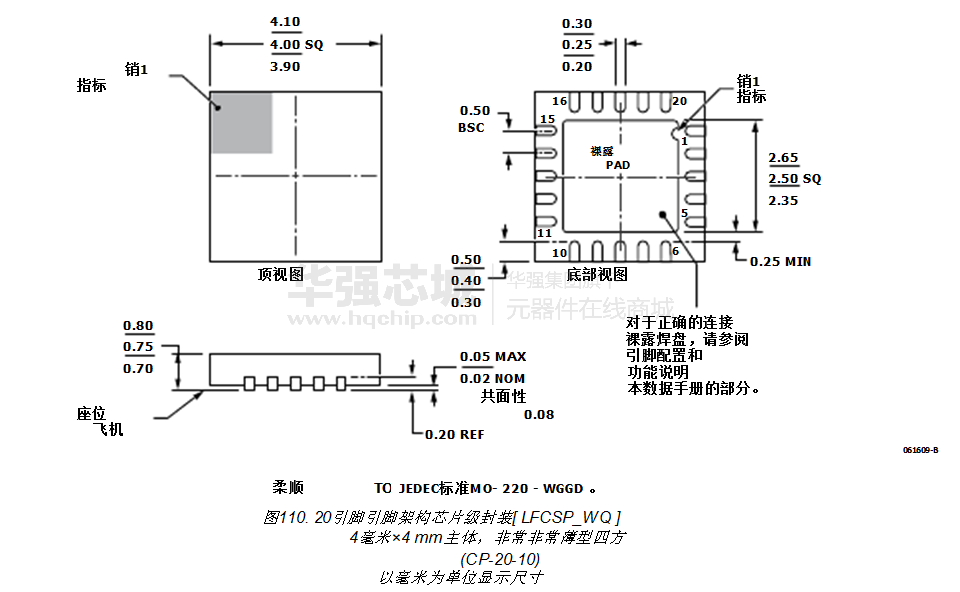

4.20引脚,采用4 mm× 4 mm LFCSP封装包

5.过流和热保护

6.软启动

7.欠压锁定

8.巴克关键指标

输出电压范围: 0.8 V至3.8 V

电流模式拓扑结构提供出色的瞬态响应

3 MHz的工作频率

峰值效率高达96%

使用小型多层电感器和电容器

模式引脚选择强制PWM或自动PWM / PSM模式

100 %占空比低压差模式

9.LDO的关键指标

输出电压范围: 0.8 V至5.2 V

低V IN从1.7 V至5.5 V

稳定的2.2 μF陶瓷输出电容器

高PSRR

低输出噪声

低压差

-40°C至+ 125°C的结温范围

电路图、引脚图和封装图

应用案例

隆利科技的MiniLED车载显示产品助力上汽非凡R7首发

2022-09-29

飞凡R7搭载京东方Mini LED车载屏,拥有2.5K分辨率

2022-09-20

搭载京东方柔性AMOLED超高清中控屏的飞凡R7正式上市

2022-05-18

联想新款笔记本搭载AMD R7 6800HS型号

2022-05-13

r7 4800h相当于i7几代?11代i7实力不负口碑

2021-11-05

锐龙r7和酷睿i7哪个好?电脑CPU选择建议

2021-10-28

联想拯救者刃7000P 2021官宣:R7 5800加持 全景侧透

2021-02-24

让工作与娱乐兼顾,同r7 3700x相比搭载i7-10700电脑更从容!

2021-02-22