AD807

155 Mbps、低功耗、后置放大器/时钟和数据恢复IC

制造商:ADI/AD

产品信息

优势和特点

满足CCITT G.958 STM-1再生器—A型要求

满足Bellcore TR-NWT-000253 OC-3要求

155 Mbps 时钟恢复和数据重定时

接受NRZ数据,无需前同步码

锁相环型时钟恢复,无需晶振

量化器灵敏度:2 mV

输出抖动:2.0°(均方根)

电平检测范围:2.0 mV至30 mV

单电源供电:+5 V或–5.2 V

低功耗:170 mW

10 KH ECL/PECL 兼容输出

封装:16引脚窄体150 Mil SOIC

产品详情

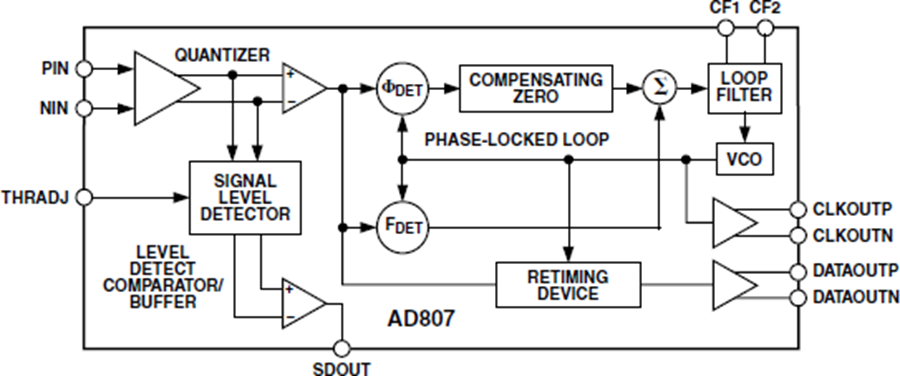

AD807可提供四种接收器功能:数据量化、信号电平检测、时钟恢复和数据重定时,适用于155 Mbps NRZ数据。该器件连同PIN二极管/前置放大器组合,可以用于高度集成、低成本、低功耗SONET OC-3或SDH STM-1光纤接收器。

当输入信号电平降至用户可调阈值以下时,接收器前端信号电平检测电路会予以提示。该阈值通过一个外部电阻设置。信号电平检测电路的3 dB光学迟滞可防止信号电平检测输出颤振。

PLL具有经工厂调整的VCO中心频率和频率采集控制环路,二者配合可保证频率采集无假锁。这样便无需依赖晶振或SAW滤波器等外部器件来协助频率采集。

AD807利用两个控制环路采集输入数据的频率和相位锁定,无需外部控制。首先由频率采集控制环路采集输入数据的频率,无需前同步码便可采集到随机或加扰数据的频率锁定。在锁频状态,频率误差为0,鉴频器无进一步影响。然后,相位采集控制环路开始工作,确保输出相位跟踪输入相位。所用鉴相器已取得专利,几乎可消除AD807整个器件的码抖动。

VCO采用环形振荡器结构以及低噪声专利设计技术。抖动为2.0°(均方根)。正是采用完全差分信号结构,电源抑制比电路,以及使IC不受外来信号干扰的介质隔离工艺才得以实现低抖动特性。该器件可承受数百毫伏的电源噪声,而抖动性能则不受影响。

环路阻尼由阻尼系数电容的值决定,用户通过选择该电容设置PLL的抖动峰值和采集时间。当阻尼系数为5或更大时,可轻松满足CCITT G.958 A型抖动传递要求。

器件设计可保证在无输入数据转换时,时钟输出频率的漂移小于20%。将阻尼系数电容CD短路,可使时钟输出频率变为VCO中心频率。

AD807采用+5 V或–5.2 V单电源供电,功耗为140 mW。

电路图、引脚图和封装图

在线购买

型号:AD807A-155BRZRL7

描述:-

型号:AD807A-155BRZRL

描述:-

型号:AD807A-155BRZ

描述:-

型号:AD807A-155BRRL7

描述:-

型号:AD807A-155BRRL

描述:-

型号:AD807A-155BR

描述:-

技术资料

应用案例

诺基亚2.3将在印度上架 官方售价约合人民币807元

2019-12-20

樱花锁业DZ-8077E电子锁简介

2020-01-07

同创新佳科技LS-8078-MF酒店锁简介

2019-12-06

同创新佳科技LS-8076-FMT智能门锁介绍

2019-12-09

同创新佳科技LS-8077-FMT公寓智能门锁介绍

2019-12-09

BC807-40,215(Nexperia)双极结型晶体管中文资料_封装尺寸_回流焊脚信息

2024-09-07

AD807 155 Mbps、低功耗、后置放大器/时钟和数据恢复IC技术手册

2025-04-15

OpenWrt 23.05开源Linux操作系统用于路由器和资源受限的无头嵌入式系统

2023-10-17