74LS373

三态输出的八 D 锁存器

制造商:

产品信息

373 的输出端 Q0~Q7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,Q0~Q7为正常逻辑状态,可用来驱动负载或总线。当 OE 为高电平时,Q0~Q7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端 LE 为高电平时,Q 随数据 D 而变。当 LE 为低电平时,D 被锁存在已建立的数据电平。当 LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善 400mV。

优势特点

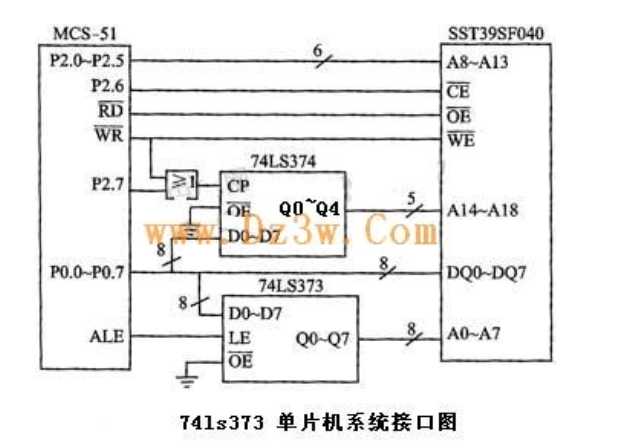

74LS373在单片机扩展系统中的典型应用电路

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端G为高电平时,输出Q0-Q7的状态与输入端D1-D7状态相同;当G发生负的跳变时,输入端D0-D7 数据锁入Q0-Q7。51单片机的ALE信号可以直接与74LS373的G连接。在MCS-51单片机系统中,其连接方法如下图所示。其中输入端1D-8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示三态输出门一直导通,可以送出地址信号。

规格参数

引出端:

D0~D7 数据输入端

OE 三态允许控制端(低电平有效)

Q0~Q7 输出端

真值表:

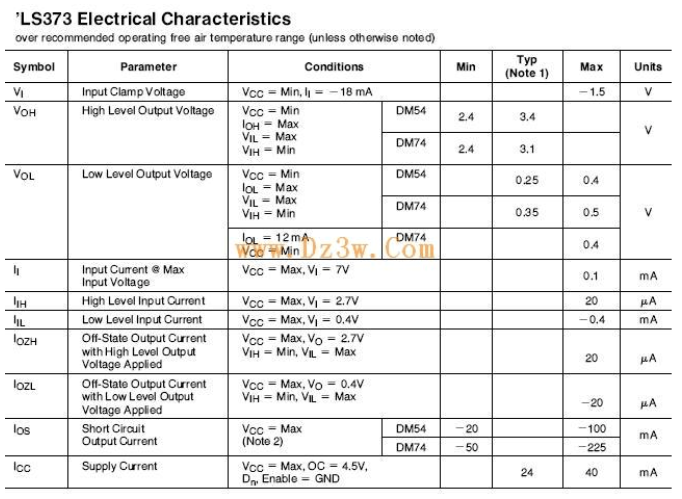

电气参数:

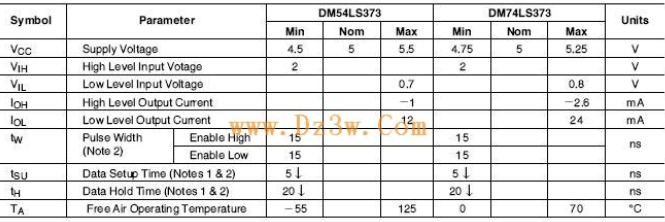

推荐工作条件: