74HC373

具有三态输出的八路透明D类锁存器

制造商:

产品信息

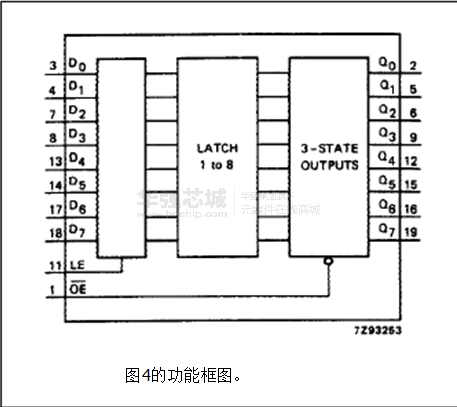

74HC373是一款高速CMOS器件,74HC373引脚兼容低功耗肖特基TTL(LSTTL)系列。74HC373遵循JEDEC标准no.7A。 74HC373是八路D 型锁存器,每个锁存器具有独立的D 型输入,以及适用于面向总线的应用的三态输出。所有锁存器共用一个锁存使能(LE)端和一个输出使能(OE)端。 74HC373包含八个具有三态输出的D 型透明锁存器。当LE为高时,数据从Dn输入到锁存器,在此条件下,锁存器进入透明模式,也就是说,锁存器的输出状态将会随着对应的D输入每次的变化而改变。当LE为低时,锁存器将存储D输入上的信息一段就绪时间,直到LE的下降沿来临。 当OE为低时,8个锁存器的内容可被正常输出;当OE为高时,输出进入高阻态。OE端的操作不会影响锁存器的状态。 74HC373与以下型号逻辑功能相同: -74HC533,但输出为反相 -74HC563,但输出为反相且引脚布局不同 -74HC573,但引脚布局不同

优势特点

结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):

型号 tPd PD

54S373/74S373 7ns 525mW

54LS373/74LS373 17ns 120mW

373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用

74HC373

来驱动负载或总线。

当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但

锁存器内部的逻辑操作不受影响。

当锁存允许端 LE 为高电平时,O 随数据 D 而变。当 LE 为低电平时,O 被锁存在已建立的数据电平。

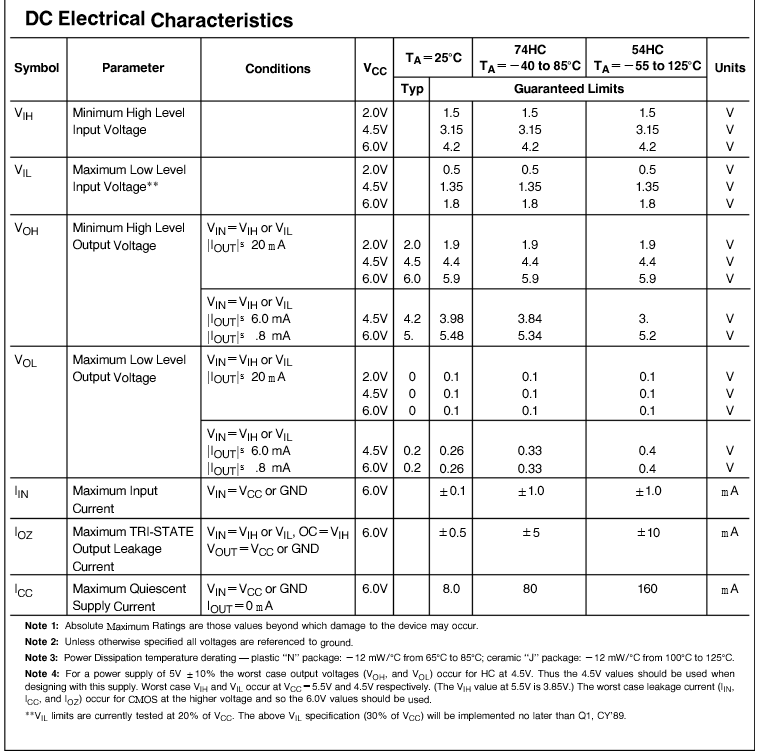

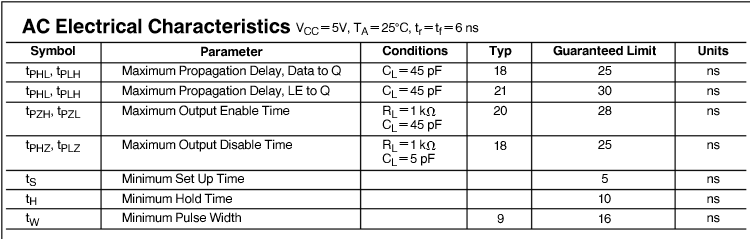

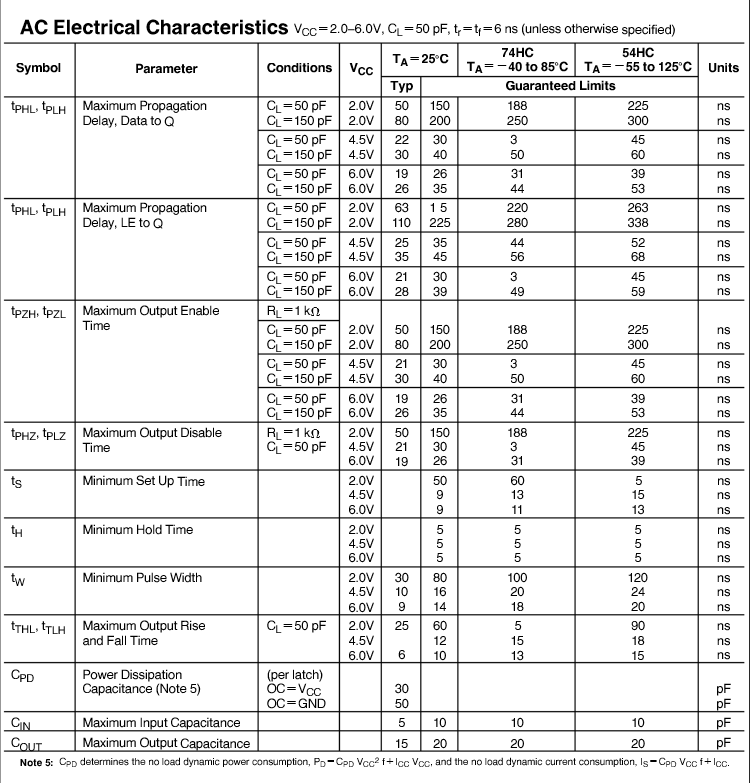

规格参数

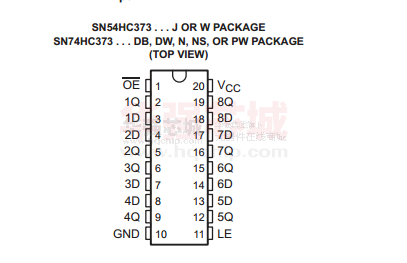

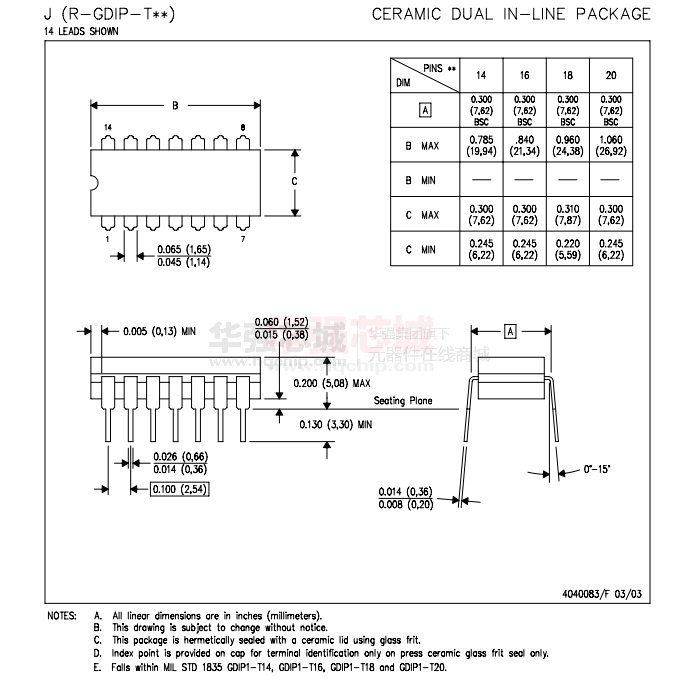

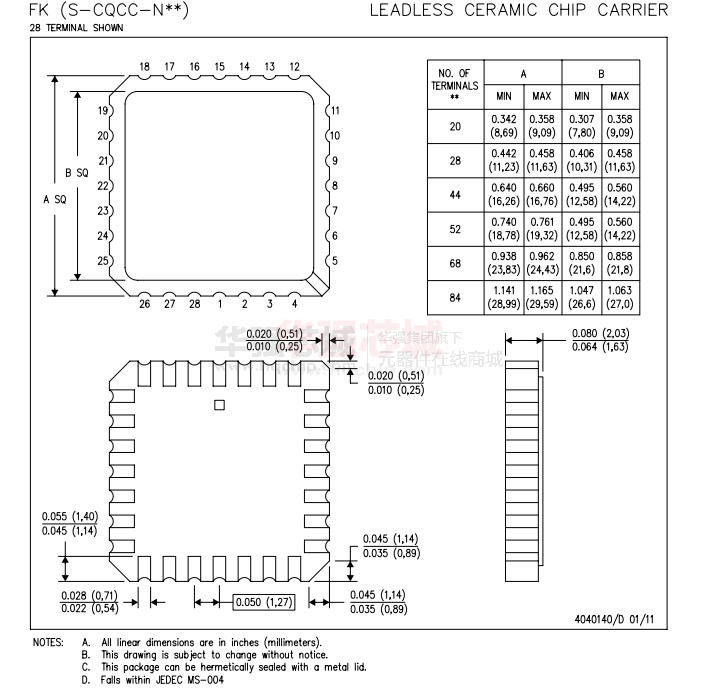

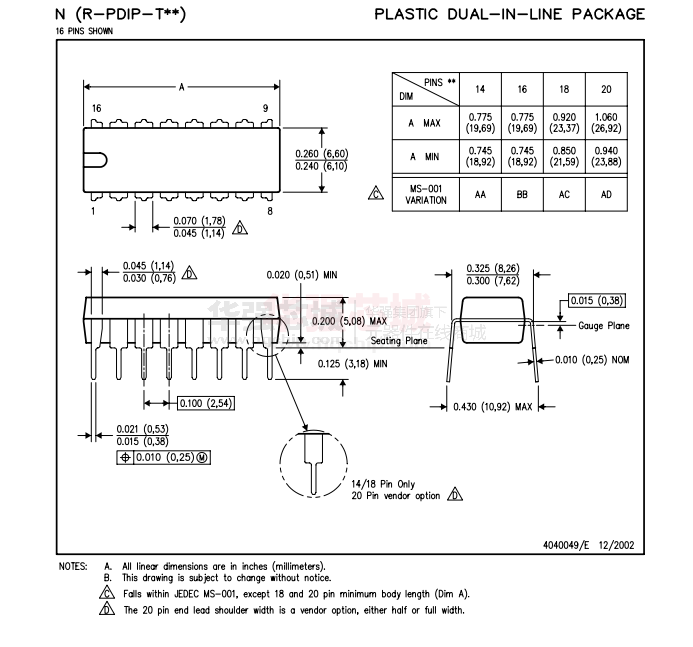

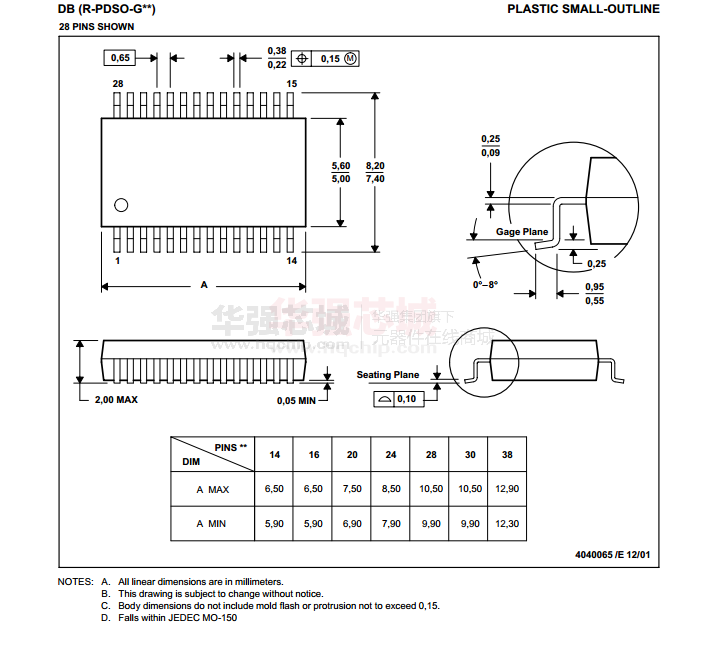

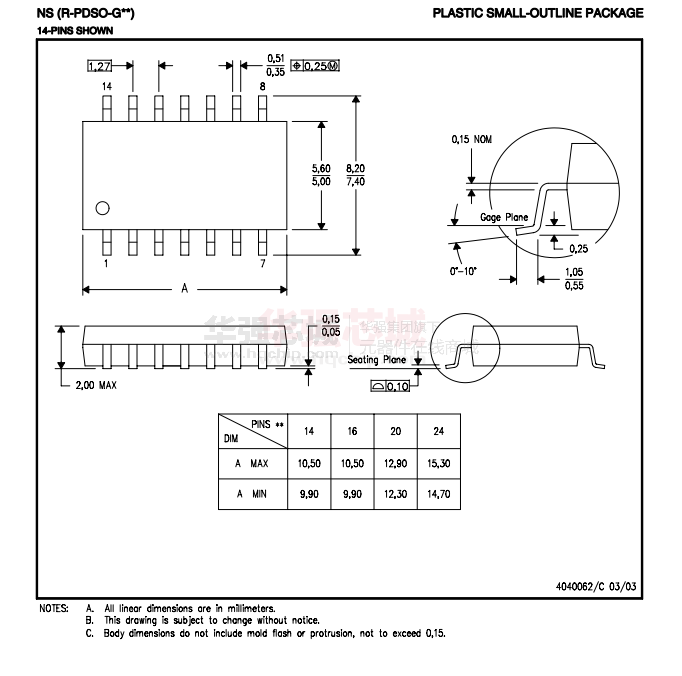

电路图、引脚图和封装图

在线购买

型号:74HC373

描述:-

型号:74HC373BQ.115

描述:-

型号:74HC373PW.118

描述:-

型号:74HC373N.652

描述:-

型号:74HC373D.653

描述:-

型号:74HC373DB.118

描述:-